Whilst looking up the introduction date of the first PAL devices on Wikipedia (Monolithic Memories MMI in 1978) I fell down one of those internet rabbit-holes, which led to the discovery of the Naked Milli 16-bit TTL computer.

The Wikipedia entry on Programmable Logic mentioned an engineer called John Birkner, who managed the PAL project at MMI, but before that he had designed a 16-bit TTL minicomputer for Computer Automation Inc. of Irvine, California.

A bit more googling and I found the videos and transcript of his Oral History, recorded at the Computer History Museum - some 4 years ago.

Apparently, his 16-bit TTL computer used only 80 standard logic devices - which immediately whetted my appetite - because that is about the chip count I am working towards for my Suite-16 design.

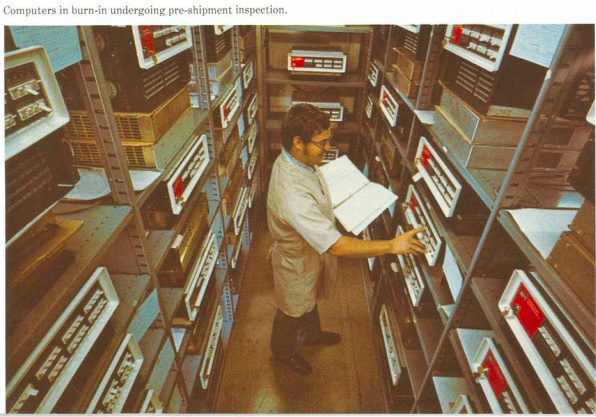

The people at Computer Automation were doing a line of minicomputers that were intended for incorporation into OEM products, and as such were stripped down to a bare chassis with no outer casing or front panel.

The marketing team at CAI decided to call this range - the naked mini, and for whatever reasons, in the mid 1970s that seemed to appeal to their customers.

John Birkner was given the task to reduce the size of the machine from 3 15"x17" boards to a half-size board just 15" x 7". This he did by basing his cpu around a 74181 4-bit alu, bitslice design and microcoded using MMI PROMs to hold the microcode.

The resulting machine was marketed as the Naked Milli - and one key customer was Barclays Bank, who were just starting to introduce a new generation of ATMs. The small size of the machine suited the ATM application, allowing a fully featured cash dispensing terminal, and presumably a bigger cash dispensing box!

Birkner realised by 1976, that the days of TTL cpus was rapidly coming to an end, and decided that he should join a “chip company”.

Thus began a relationship with MMI which led to him being hired to manage their PAL project.

Here’s the link to the Naked Milli marketing brochure:

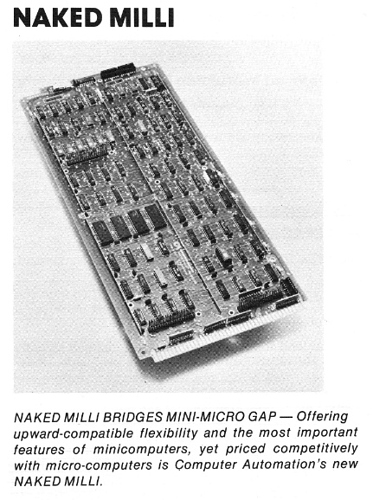

The photograph in the marketing brochure shows the cpu board - and you can clearly count the IC packages - approximately 80, especially the larger 74181s that make up the bitslice ALU.

Notable is the chip layout, 4 parallel rows of ICs on each half of the board that emphasises the bitslice design.

As well as the CPU there was also a similar sized I/O card, which handled a wide range of peripherals including disks, tapes, CRT terminals and Teletypes.

By today’s standards not a particularly fast machine with an instruction cycle time of 6uS plus depending on the addressing mode.