This nice analysis was linked in a Q&A about the demise of the 68000 architecture:

Updated addressing mode table, John Mashey, comp.arch, 1993-04-06

(which is a revised followup to Addressing modes (long) from 1993-03-05)

There’s an easier to read version here

John Mashey on RISC/CISC

One nice thing about it is it being quantitative, and including incidentally a survey of architectures at the time:

CPU Age 3a 3b 3c 3d 4a 4b 5a 5b 6a 6b # ODD

RULE 4 >3

-------------------------------------------------------------------------

A1 4 1 4 1 0 0 1 0 1 8 3+ 1 AMD 29K

B1 5 1 4 1 0 0 1 0 1 5 4 - R2000

C1 2 1 4 2 0 0 1 0 1 5 4 - SPARC

D1 2 1 4 3 0 0 1 0 1 5 0+ 1 MC88000

E1 5 1 4 10+ 0 0 1 0 1 5 4 1 HP PA

F1 5 2+ 4 1 0 0 1 0 1 4+ 3+ 3 IBM RT/PC

G1 1 1 4 4 0 0 1 1 1 5 5 - IBM RS/6000

H1 2 1 4 4 0 0 1 0 1 5 4 - Intel i860

---------------------------------------------------------------

L4 26 4 8 2* 0* 1 2 2 4 4 2 2 IBM 3090

M2 12 12 12 15 0* 1 2 2 4 3 3 1 Intel i486

N1 10 21 21 23 1 1 2 2 4 3 3 - NSC 32016

O3 11 11 22 44 1 1 2 2 8 4 3 - MC 68040

P3 13 56 56 22 1 1 6 2 24 4 0 - VAX

A couple more appear later:

let me add the two cases that I knew of that were more

on the borderline: i960 and Clipper:

CPU Age 3a 3b 3c 3d 4a 4b 5a 5b 6a 6b # ODD

RULE 4 >3

-------------------------------------------------------------------------

J1 5 4+ 8+ 9+ 0 0 1 0 2 4+ 3+ 5 Clipper

K1 3 2+ 8+ 9+ 0 0 1 2+ - 5 3+ 5 Intel 960KB

I missed seeing ARM in there, but it’s in the revision in a table which aims to count addressing modes:

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22

r r

r r r +d1 +d1

r r r | | r r | r r+ +d +d1 I +s

r r r +d +x +s| s+ s+|s+ +d +d|r+ +d I I I +s I

r +d +x +s >r >r >r|r+ -r a a r+|-r +x +s|I I +s +s +d2 +d2 +d2

-- -- -- -- -- -- --|-- -- -- -- --|-- -- --|-- -- -- -- --- --- ---

AMD 29K 1 | | |

Rxxx 1 | | |

SPARC 1 1 | | |

88K 1 1 1 | | |

HP PA 2 1 1 4 1 1| | |

ROMP 1 2 | | |

POWER 1 1 1 1 | | |

i860 1 1 1 1 | | |

Swrdfish 1 1 1 | 1 | |

ARM 2 2 2 1 1| 1 1

Clipper 1 3 1 | 1 1 2 | |

i960KB 1 1 1 1 | 2 2 | 1 |

S/360 1 | 1 |

i486 1 3 1 1 | 1 1 2 | 2 3|

NSC32K 3 | 1 1 3 3 | 3| 9

MC68000 1 1 | 1 1 2 | 2 |

MC68020 1 1 | 1 1 2 | 2 4| 16 16

VAX 1 3 1 | 1 1 1 1 1| 1 3| 1 3 1 3

Edit: somewhere in my related adventures I found this 1992 paper by Samuel O. Aletan

An Overview of RISC Architecture (10 pages)

information which has accumulated over the years has resulted in a new philosophy about architecture design. However, the philosophy is not really new because it has been around for a long period of time. It has been the main stay of high performance architecture such as CDC 6600 and CRAY. The computer designs based on this philosophy are commonly referred to as reduced instruction set computers (RISCS). The emergence of RISC into the commercial world in the early to mid-80s has been one of the reasons contributing to the current surge in new computer architecture.

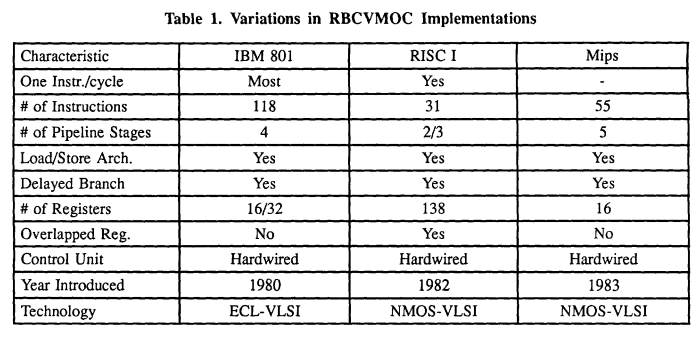

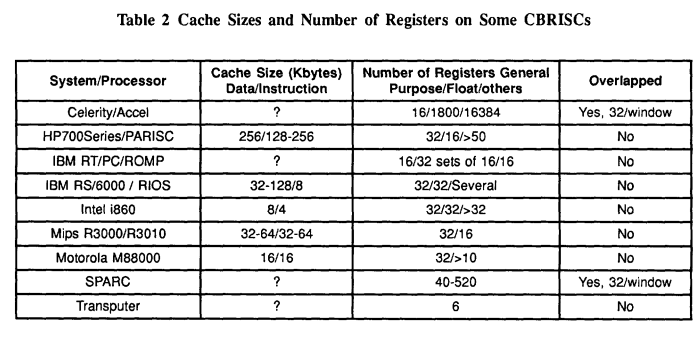

From there, a couple of tables