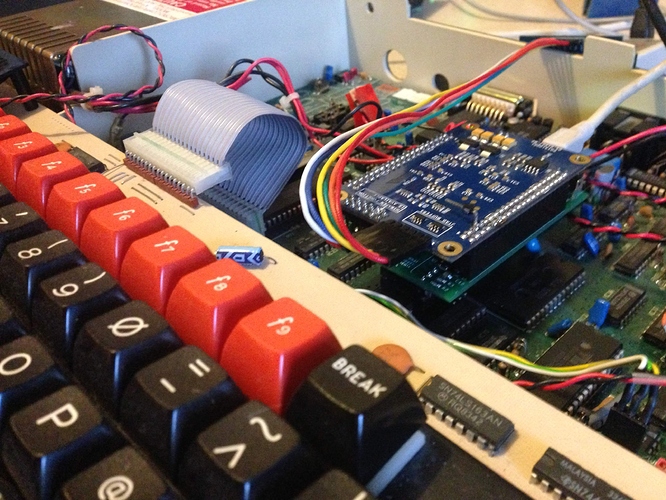

I visited @hoglet yesterday and we had a look at his In Circuit Emulator projects, which are now CPU-specific interface boards which go into the CPU socket and accept an affordable commodity FPGA board on top. There’s a board for Z80, and one for 6502 (or 65C02), and there’s one in the works for 6809. In these photos you’ll see a ZX81, a ZXSpectrum, a BBC Micro, and two second processor units for the Beeb, being a 65C02 and a Z80 respectively.

Of course, all the lids are off! Dave posts some interesting technical updates in this thread on Stardot:

ICE T65/Z80/6809

The ICE design combines an HDL model of the target CPU with a second CPU that runs a monitor program: you interact with that program over a serial connection, and it offers a rich set of commands for viewing CPU state, memory dumping, disassembly, tracing, single-stepping, breakpoints and watchpoints.

Yesterday’s session was the tail end of investigations into supporting the host system while the target CPU is halted - some hosts need to see activity so they can refresh DRAM, and need some care to accept memory reads and writes from the monitor CPU, which otherwise might not look quite like native accesses. In the case of Acorns 65C02 second processor, it needs to see regular SYNC cycles, and uses RDY to grab the bus for DRAM refresh.

The project is open source: