I found some great Perl tools including a sixbit conversion. I found that site before, but never checked the tools (but papertapes).

https://so-much-stuff.com/pdp8/tools/tools.php

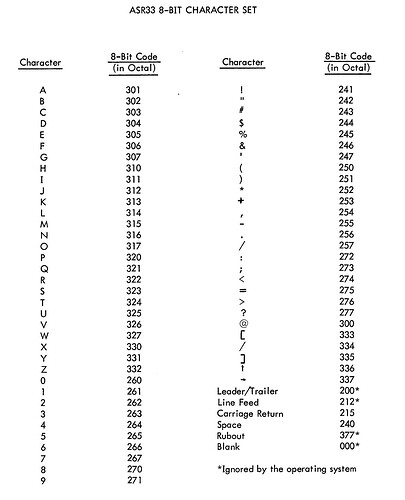

The sixbit output is different than from the online emu. Also some characters are different. And showing more characters and it’s very easy to identify larger sections of text. I can read T@APE, maybe a coincidence. The short section is from the online emu showing 2 columns. The 2 rows below are from CHEKMO chess. The string CHECKMATE WITH is harder to identify as it only uses one column.

Unfortunately, I haven’t found anything of interest on my files.

I haven’t checked all tools, yet. There should also be the 3 for 2 conversion (OS/8 disk ?).

One interesting thing is bin2c (quick pdp8 to c conversion).

0022 170)17400 14077 37417 0050 0053 25413 0077 17477 |@`?�O@(@+�K@?|?

0023 000)37406 22064 7413 5465 22046 3465 32037 32440 �F�4<K,5�&\5�_�

0023 010)23046 32046 17413 5444 32444 17425 22046 22044 �&�&|K,$�$|U�&�$

0023 020)22042 12446 22077 32444 20065 22037 3425 22037 �"T&�?�$�5�_\U�_

0023 030)22037 12444 22044 32446 3467 22046 32064 23046 �_T$�$�&\7�&�4�&

0023 040)0015 22006 21046 32446 17467 22065 32460 17444 @M�F�&�&|7�5�0|$

0023 050)17425 37464 14037 37443 6014 3070 6014 3006 |U�4`_�#0LX80LXF

0023 060)2402 32416 3006 6014 3065 33414 3006 2067 TB�NXF0LX5�LXFP7

0023 070)6064 3067 6004 3006 3006 3006 36456 4005 04X70DXFXFXF�. E

0023 100)4010 12016 2424 14406 6404 13006 5404 13026 HPNTTdF4DXF,DXV

0023 110)16436 7026 10024 10001 12005 15004 17034 16025 t^8V@T@APEhDx\pU

0023 120)3034 12416 15025 5404 7032 13031 6035 10020 X\TNhU,D8ZXY0]@P

0023 130)5413 10010 24461 10020 22471 10020 2011 10004 ,K@H�1@P�9@PPI@D

0023 140)21410 14431 3063 6031 4425 17024 5420 15032 �HdYX30Y$UxT,PhZ

0023 150)5413 14432 12011 7013 6404 12024 7024 12025 ,KdZPI8K4DPT8TPU

0023 160)4431 13024 16406 6413 7011 16431 0004 7000 $YXTtF4K8ItY@D8@

0023 170)25016 2431 23007 3452 0444 23067 0046 0051 �NTY�G*D$�7@&@)

0024 000)23041 22044 23041 32044 23007 3444 20407 0044 �!�$�!�$�G$�G@$

0024 010)22025 2442 22044 23025 12444 23025 12425 22044 �UT"�$�UT$�UTU�$

0024 020)22065 33444 23046 33444 7407 30054 32047 7475 �5�$�&�$<G�,�’<=

04600 0677 F> | a4600, AND I M4677

04601 6444 3$ | a4601, IOT 0444

04602 1317 KO | a4602, TAD M4717

04603 6513 4K | a4603, IOT 0513

04604 4644 &$ | a4604, JMS I C4644

04605 6507 4G | a4605, IOT 0507

04705 0626 FV | a4705, AND I M4626

04706 0413 DK | a4706, AND I M13

04707 2626 VV | a4707, ISZ I M4626

04710 3635 ^] | a4710, DCA I M4635

04711 2616 VN | a4711, ISZ I M4616

04712 2420 TP | a4712, ISZ I M20

04713 0120 AP | a4713, AND M120

04714 0524 ET | a4714, AND I M124

04715 0432 DZ | a4715, AND I M32

04716 3436 ^ | a4716, DCA I M36

0026 120)1403 1410 1405 1403 1413 1415 1401 1424 LCLHLELCLKLMLALT

0026 130)1005 1440 1427 1411 1424 1010 0040 65000 HEL LWLILTHH@ �@

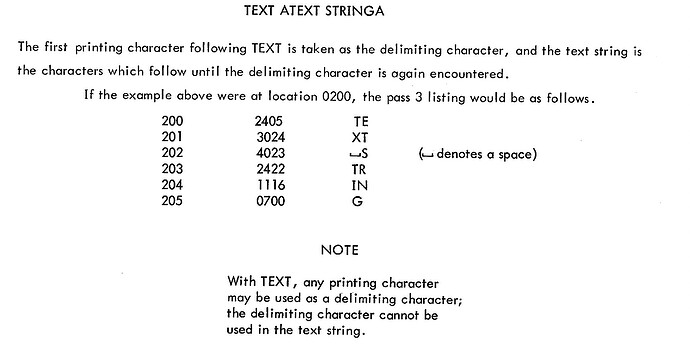

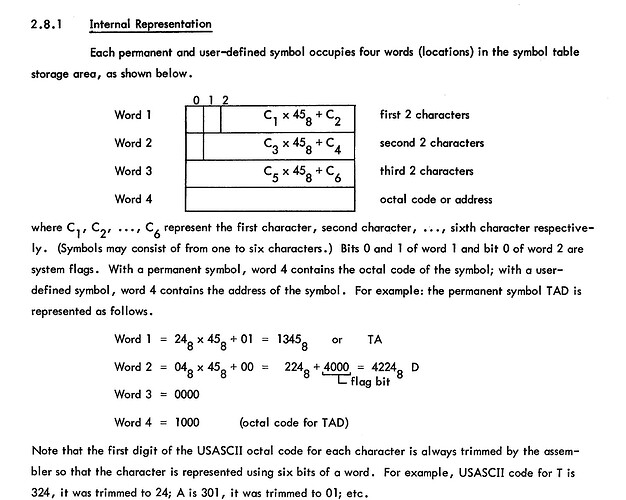

Earlier, I found Radix 45, not 40 ot 50. But that should be only internally on a PAL assembler. No or very few results on Google.