Yes, thanks, the Intersil is a bit different. There are 6 600x IOT opcodes. But none of my recent ROM combinations have any of those near the beginning of a run. Some more special opcodes are in the source of bindump (6120 tools). This Control panel service routine is interesting. It’s (starting) at 7777 of the ROM. Maybe only for memory larger than 4K.

So at 7777 must be 6000. The PC is stored at 0000 of the “panel memory”.

At 7777 I have 0006 (pair 4-8). Would be 6000 when bit reversed! Maybe that’s the reason for bit reversal of the 6120. I will check this. There are some more Intersil specials like extended memory, octal debugging tool etc but I don’t have any of these Intersil ICs.

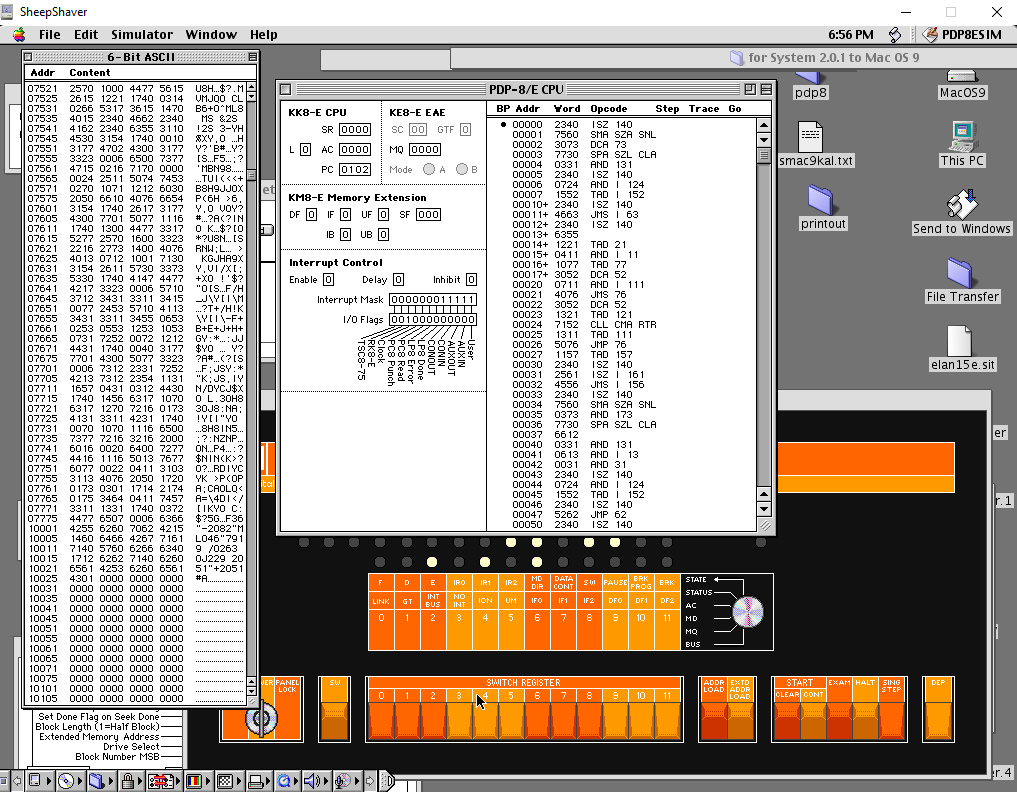

The Mac emulator replaces the word at 7777 with 5370 (JMP 7770). I don’t know why. With empty bytes at the end this is wrong. Maybe with relocation or if the empty sections are replaced.

I’ve tested some more ROM combinations. Only few are plausible, not mixing with the empty bytes. All codes when starting at 0. 200 or vector 7777 make less sense. Still no strings.

5-1, 6-2, 7-3, 8-4. (7777: 0600) swapped ROM in pairs, previously pairs were 1-5, 2-6, 3-7, 4-8. 2340->4023. Also quite plausible. At least all not running into the auto-index. All end up in full loops shown.

[0000] IRQ,DLY,IE=0,1,0 L/AC:0/0000 MQ:0000 IR:4023 JMS 0023 ;Jump to subroutine ZP 0023

[0024] IRQ,DLY,IE=0,0,0 L/AC:0/0000 MQ:0000 IR:5271 JMP @@71 ;Jump Current page @@71

[0071] IRQ,DLY,IE=0,0,0 L/AC:0/0000 MQ:0000 IR:1077 TAD 0077 ;Add operand to AC, ZP 0077

[0072] IRQ,DLY,IE=0,0,0 L/AC:0/3112 MQ:0000 IR:7650 SNA CLA ;Skip on AC <> 0, Clear AC

[0074] IRQ,DLY,IE=0,0,0 L/AC:0/0000 MQ:0000 IR:5235 JMP @@35 ;Jump Current page @@35

[0035] IRQ,DLY,IE=0,0,0 L/AC:0/0000 MQ:0000 IR:7303 CLL CLA IAC BSW;Clear L, set AC to 0100

[0036] IRQ,DLY,IE=0,0,0 L/AC:0/0100 MQ:0000 IR:3077 DCA 0077 ;Deposit AC to memory then clear AC, ZP 0077

[0037] IRQ,DLY,IE=0,0,0 L/AC:0/0000 MQ:0000 IR:1266 TAD @@66 ;Add operand to AC, Current page @@66

[0040] IRQ,DLY,IE=0,0,0 L/AC:0/0005 MQ:0000 IR:3103 DCA 0103 ;Deposit AC to memory then clear AC, ZP 0103

[0041] IRQ,DLY,IE=0,0,0 L/AC:0/0000 MQ:0000 IR:1306 TAD @@06 ;Add operand to AC, Current page @@06

[0042] IRQ,DLY,IE=0,0,0 L/AC:0/3360 MQ:0000 IR:3100 DCA 0100 ;Deposit AC to memory then clear AC, ZP 0100

[0043] IRQ,DLY,IE=0,0,0 L/AC:0/0000 MQ:0000 IR:4023 JMS 0023 ;Jump to subroutine ZP 0023

[0024] IRQ,DLY,IE=0,0,0 L/AC:0/0000 MQ:0000 IR:5271 JMP @@71 ;Jump Current page @@71

starting at 600 vector at 7777

[0600] IRQ,DLY,IE=0,1,0 L/AC:0/0000 MQ:0000 IR:0000 AND 0000 ;AND operand with AC, ZP 0000

[0601] IRQ,DLY,IE=0,1,0 L/AC:0/0000 MQ:0000 IR:2000 ISZ 0000 ;Increment operand and skip if zero, ZP 0000

[0602] IRQ,DLY,IE=0,1,0 L/AC:0/0000 MQ:0000 IR:1103 TAD 0103 ;Add operand to AC, ZP 0103

[0603] IRQ,DLY,IE=0,1,0 L/AC:0/0062 MQ:0000 IR:3054 DCA 0054 ;Deposit AC to memory then clear AC, ZP 0054

[0604] IRQ,DLY,IE=0,1,0 L/AC:0/0000 MQ:0000 IR:1104 TAD 0104 ;Add operand to AC, ZP 0104

[0605] IRQ,DLY,IE=0,1,0 L/AC:0/7770 MQ:0000 IR:3133 DCA 0133 ;Deposit AC to memory then clear AC, ZP 0133

[0606] IRQ,DLY,IE=0,1,0 L/AC:0/0000 MQ:0000 IR:1105 TAD 0105 ;Add operand to AC, ZP 0105

[0607] IRQ,DLY,IE=0,1,0 L/AC:0/5673 MQ:0000 IR:7650 SNA CLA ;Skip on AC <> 0, Clear AC

[0611] IRQ,DLY,IE=0,1,0 L/AC:0/0000 MQ:0000 IR:7327 STL CLA IAC RTL;Set L, Set AC to 0001, Rotate AC & L left twice

[0612] IRQ,DLY,IE=0,1,0 L/AC:0/0006 MQ:0000 IR:0103 AND 0103 ;AND operand with AC, ZP 0103

[0613] IRQ,DLY,IE=0,1,0 L/AC:0/0002 MQ:0000 IR:7650 SNA CLA ;Skip on AC <> 0, Clear AC

[0615] IRQ,DLY,IE=0,1,0 L/AC:0/0000 MQ:0000 IR:1310 TAD @@10 ;Add operand to AC, Current page @@10

[0616] IRQ,DLY,IE=0,1,0 L/AC:0/1000 MQ:0000 IR:3060 DCA 0060 ;Deposit AC to memory then clear AC, ZP 0060

[0617] IRQ,DLY,IE=0,1,0 L/AC:0/0000 MQ:0000 IR:1054 TAD 0054 ;Add operand to AC, ZP 0054

[0620] IRQ,DLY,IE=0,1,0 L/AC:0/0062 MQ:0000 IR:1304 TAD @@04 ;Add operand to AC, Current page @@04

[0621] IRQ,DLY,IE=0,1,0 L/AC:1/0053 MQ:0000 IR:7640 SZA CLA ;Skip on AC = 0, Clear AC

[0622] IRQ,DLY,IE=0,1,0 L/AC:1/0000 MQ:0000 IR:5263 JMP @@63 ;Jump Current page @@63

[0663] IRQ,DLY,IE=0,0,0 L/AC:1/0000 MQ:0000 IR:1133 TAD 0133 ;Add operand to AC, ZP 0133

[0664] IRQ,DLY,IE=0,0,0 L/AC:1/7770 MQ:0000 IR:7106 CLL RTL ;Clear L, Rotate AC & L left twice

[0665] IRQ,DLY,IE=0,0,0 L/AC:1/7741 MQ:0000 IR:7006 RTL ;Rotate AC & L left twice

[0666] IRQ,DLY,IE=0,0,0 L/AC:1/7607 MQ:0000 IR:0035 AND 0035 ;AND operand with AC, ZP 0035

[0667] IRQ,DLY,IE=0,0,0 L/AC:1/7203 MQ:0000 IR:3055 DCA 0055 ;Deposit AC to memory then clear AC, ZP 0055

[0670] IRQ,DLY,IE=0,0,0 L/AC:1/0000 MQ:0000 IR:1133 TAD 0133 ;Add operand to AC, ZP 0133

[0671] IRQ,DLY,IE=0,0,0 L/AC:1/7770 MQ:0000 IR:7002 BSW ;Byte Swap AC

[0672] IRQ,DLY,IE=0,0,0 L/AC:1/7077 MQ:0000 IR:7112 CLL RTR ;Clear L, Rotate AC & L right twice

[0673] IRQ,DLY,IE=0,0,0 L/AC:1/5617 MQ:0000 IR:7012 RTR ;Rotate AC & L right twice

[0674] IRQ,DLY,IE=0,0,0 L/AC:1/7343 MQ:0000 IR:7010 RAR ;Rotate AC & L right

[0675] IRQ,DLY,IE=0,0,0 L/AC:1/7561 MQ:0000 IR:0311 AND @@11 ;AND operand with AC, Current page @@11

[0676] IRQ,DLY,IE=0,0,0 L/AC:1/3560 MQ:0000 IR:7421 MQL ;Load MQ from AC then clear AC

[0677] IRQ,DLY,IE=0,0,0 L/AC:1/0000 MQ:3560 IR:1133 TAD 0133 ;Add operand to AC, ZP 0133

[0700] IRQ,DLY,IE=0,0,0 L/AC:1/7770 MQ:3560 IR:0035 AND 0035 ;AND operand with AC, ZP 0035

[0701] IRQ,DLY,IE=0,0,0 L/AC:1/7300 MQ:3560 IR:7501 MQA ;OR MQ with AC

[0702] IRQ,DLY,IE=0,0,0 L/AC:1/7760 MQ:3560 IR:3052 DCA 0052 ;Deposit AC to memory then clear AC, ZP 0052

[0703] IRQ,DLY,IE=0,0,0 L/AC:1/0000 MQ:3560 IR:5020 JMP 0020 ;Jump ZP 0020

[0020] IRQ,DLY,IE=0,0,0 L/AC:1/0000 MQ:3560 IR:1107 TAD 0107 ;Add operand to AC, ZP 0107

[0021] IRQ,DLY,IE=0,0,0 L/AC:1/5612 MQ:3560 IR:7640 SZA CLA ;Skip on AC = 0, Clear AC

[0022] IRQ,DLY,IE=0,0,0 L/AC:1/0000 MQ:3560 IR:5230 JMP @@30 ;Jump Current page @@30

[0030] IRQ,DLY,IE=0,0,0 L/AC:1/0000 MQ:3560 IR:4023 JMS 0023 ;Jump to subroutine ZP 0023

[0024] IRQ,DLY,IE=0,0,0 L/AC:1/0000 MQ:3560 IR:5271 JMP @@71 ;Jump Current page @@71

[0071] IRQ,DLY,IE=0,0,0 L/AC:1/0000 MQ:3560 IR:1077 TAD 0077 ;Add operand to AC, ZP 0077

[0072] IRQ,DLY,IE=0,0,0 L/AC:1/3112 MQ:3560 IR:7650 SNA CLA ;Skip on AC <> 0, Clear AC

[0074] IRQ,DLY,IE=0,0,0 L/AC:1/0000 MQ:3560 IR:5235 JMP @@35 ;Jump Current page @@35

[0035] IRQ,DLY,IE=0,0,0 L/AC:1/0000 MQ:3560 IR:7303 CLL CLA IAC BSW;Clear L, set AC to 0100

[0036] IRQ,DLY,IE=0,0,0 L/AC:0/0100 MQ:3560 IR:3077 DCA 0077 ;Deposit AC to memory then clear AC, ZP 0077

[0037] IRQ,DLY,IE=0,0,0 L/AC:0/0000 MQ:3560 IR:1266 TAD @@66 ;Add operand to AC, Current page @@66

[0040] IRQ,DLY,IE=0,0,0 L/AC:0/0005 MQ:3560 IR:3103 DCA 0103 ;Deposit AC to memory then clear AC, ZP 0103

[0041] IRQ,DLY,IE=0,0,0 L/AC:0/0000 MQ:3560 IR:1306 TAD @@06 ;Add operand to AC, Current page @@06

[0042] IRQ,DLY,IE=0,0,0 L/AC:0/3360 MQ:3560 IR:3100 DCA 0100 ;Deposit AC to memory then clear AC, ZP 0100

[0043] IRQ,DLY,IE=0,0,0 L/AC:0/0000 MQ:3560 IR:4023 JMS 0023 ;Jump to subroutine ZP 0023

[0024] IRQ,DLY,IE=0,0,0 L/AC:0/0000 MQ:3560 IR:5271 JMP @@71 ;Jump Current page @@71

[0071] IRQ,DLY,IE=0,0,0 L/AC:0/0000 MQ:3560 IR:1077 TAD 0077 ;Add operand to AC, ZP 0077

Having empty bytes at the beginning is very unlikely but having these at the end is better (although not having a vector then at 7777). 4-8, 3-7, 2-6, 1-5 has no plausible code.

(4-8, 3-7, 2-6, 1-5 (words reversed, empty bytes at end), HLT and illegal opcode 7755, looks more like data than opcodes.)

8-4, 7-3, 6-2, 5-1 (words reversed), undocumented IOT 6230. 6230, 6130, 6030 5230, 1130 are more likely data.

[0000] IRQ,DLY,IE=0,1,0 L/AC:0/0000 MQ:0000 IR:7657 CLA SAM ;Clear AC, Subtract AC from MQ

[0001] IRQ,DLY,IE=0,1,0 L/AC:0/0000 MQ:0000 IR:0004 AND 0004 ;AND operand with AC, ZP 0004

[0002] IRQ,DLY,IE=0,1,0 L/AC:0/0000 MQ:0000 IR:7435 MQL ASR ;Arithmetic shift right

[0003] IRQ,DLY,IE=0,1,0 L/AC:0/0000 MQ:0000 IR:2050 ISZ 0050 ;Increment operand and skip if zero, ZP 0050

[0004] IRQ,DLY,IE=0,1,0 L/AC:0/0000 MQ:0000 IR:6230 ;

[0005] IRQ,DLY,IE=0,1,0 L/AC:0/0000 MQ:0000 IR:6130 CLZE ;DK8-EC: Clear Clock Enable Register per AC

[0006] IRQ,DLY,IE=0,1,0 L/AC:0/0000 MQ:0000 IR:6030 KCF ;KL8-E: Clear Keyboard Flag

[0007] IRQ,DLY,IE=0,1,0 L/AC:0/0000 MQ:0000 IR:5230 JMP @@30 ;Jump Current page @@30

[0030] IRQ,DLY,IE=0,0,0 L/AC:0/0000 MQ:0000 IR:1130 TAD 0130 ;Add operand to AC, ZP 0130

[0031] IRQ,DLY,IE=0,0,0 L/AC:0/3111 MQ:0000 IR:1014 TAD 0014 ;Add operand to AC, ZP 0014

[0032] IRQ,DLY,IE=0,0,0 L/AC:0/4125 MQ:0000 IR:1030 TAD 0030 ;Add operand to AC, ZP 0030

[0033] IRQ,DLY,IE=0,0,0 L/AC:0/5255 MQ:0000 IR:1714 TAD I @@14 ;Add operand to AC, Indexed Current page @@14

[0034] IRQ,DLY,IE=0,0,0 L/AC:1/3616 MQ:0000 IR:2050 ISZ 0050 ;Increment operand and skip if zero, ZP 0050

[0035] IRQ,DLY,IE=0,0,0 L/AC:1/3616 MQ:0000 IR:3753 DCA I @@53 ;Deposit AC to memory then clear AC, Indexed Current page @@53

[0036] IRQ,DLY,IE=0,0,0 L/AC:1/0000 MQ:0000 IR:1320 TAD @@20 ;Add operand to AC, Current page @@20

[0037] IRQ,DLY,IE=0,0,0 L/AC:1/4170 MQ:0000 IR:1134 TAD 0134 ;Add operand to AC, ZP 0134

[0040] IRQ,DLY,IE=0,0,0 L/AC:0/2601 MQ:0000 IR:1014 TAD 0014 ;Add operand to AC, ZP 0014

[0041] IRQ,DLY,IE=0,0,0 L/AC:0/3615 MQ:0000 IR:1330 TAD @@30 ;Add operand to AC, Current page @@30

[0042] IRQ,DLY,IE=0,0,0 L/AC:0/6726 MQ:0000 IR:1714 TAD I @@14 ;Add operand to AC, Indexed Current page @@14

[0043] IRQ,DLY,IE=0,0,0 L/AC:1/5267 MQ:0000 IR:1130 TAD 0130 ;Add operand to AC, ZP 0130

[0044] IRQ,DLY,IE=0,0,0 L/AC:0/0400 MQ:0000 IR:1714 TAD I @@14 ;Add operand to AC, Indexed Current page @@14

[0045] IRQ,DLY,IE=0,0,0 L/AC:0/6741 MQ:0000 IR:1030 TAD 0030 ;Add operand to AC, ZP 0030

[0046] IRQ,DLY,IE=0,0,0 L/AC:1/0071 MQ:0000 IR:1714 TAD I @@14 ;Add operand to AC, Indexed Current page @@14

[0047] IRQ,DLY,IE=0,0,0 L/AC:1/6432 MQ:0000 IR:7707 ACL DVI ;Load MQ into AC, Divide

[0050] IRQ,DLY,IE=0,0,0 L/AC:1/0000 MQ:0000 IR:0110 AND 0110 ;AND operand with AC, ZP 0110

[0051] IRQ,DLY,IE=0,0,0 L/AC:1/0000 MQ:0000 IR:4777 JMS I @@77 ;Jump to subroutine Indexed Current page @@77

[2714] IRQ,DLY,IE=0,0,0 L/AC:1/0000 MQ:0000 IR:1077 TAD 0077 ;Add operand to AC, ZP 0077

[2715] IRQ,DLY,IE=0,0,0 L/AC:1/3430 MQ:0000 IR:5512 JMP I 0112 ;Jump Indexed ZP 0112

[3111] IRQ,DLY,IE=0,0,0 L/AC:1/3430 MQ:0000 IR:4076 JMS 0076 ;Jump to subroutine ZP 0076

[0077] IRQ,DLY,IE=0,0,0 L/AC:1/3430 MQ:0000 IR:3430 DCA I 0030 ;Deposit AC to memory then clear AC, Indexed ZP 0030

[0100] IRQ,DLY,IE=0,0,0 L/AC:1/0000 MQ:0000 IR:3013 DCA 0013 ;Deposit AC to memory then clear AC, ZP 0013

[0101] IRQ,DLY,IE=0,0,0 L/AC:1/0000 MQ:0000 IR:5531 JMP I 0131 ;Jump Indexed ZP 0131

[0753] IRQ,DLY,IE=0,0,0 L/AC:1/0000 MQ:0000 IR:3154 DCA 0154 ;Deposit AC to memory then clear AC, ZP 0154

[0754] IRQ,DLY,IE=0,0,0 L/AC:1/0000 MQ:0000 IR:4630 JMS I @@30 ;Jump to subroutine Indexed Current page @@30

[1051] IRQ,DLY,IE=0,0,0 L/AC:1/0000 MQ:0000 IR:3211 DCA @@11 ;Deposit AC to memory then clear AC, Current page @@11

[1052] IRQ,DLY,IE=0,0,0 L/AC:1/0000 MQ:0000 IR:3753 DCA I @@53 ;Deposit AC to memory then clear AC, Indexed Current page @@53